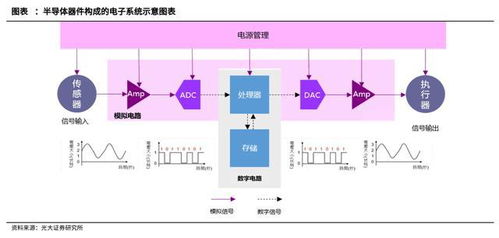

模擬CMOS集成電路設(shè)計是現(xiàn)代電子系統(tǒng)的核心,其性能直接影響到通信、傳感器、電源管理等諸多領(lǐng)域。在眾多設(shè)計技術(shù)中,虛零點法作為一種重要的頻率補(bǔ)償與穩(wěn)定性提升手段,在運算放大器、濾波器等關(guān)鍵模塊的設(shè)計中扮演著至關(guān)重要的角色。

虛零點法的基本概念

虛零點,顧名思義,是指在復(fù)平面s域上,傳遞函數(shù)中引入的一個位于右半平面(即具有正實部)的零點。這與傳統(tǒng)追求左半平面零點以改善穩(wěn)定性的直覺相悖。其核心原理在于,通過精心設(shè)計,這個“有害”的右半平面零點可以與系統(tǒng)原有的極點相互作用,從而在特定頻率范圍內(nèi)改善相位裕度,擴(kuò)展帶寬,或優(yōu)化瞬態(tài)響應(yīng)。

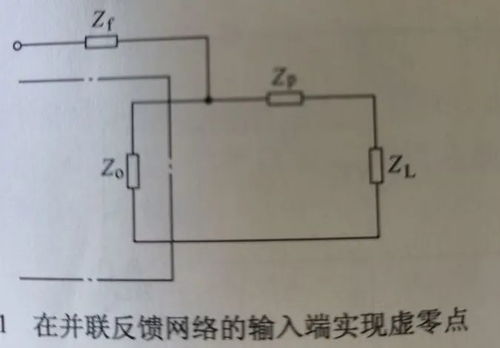

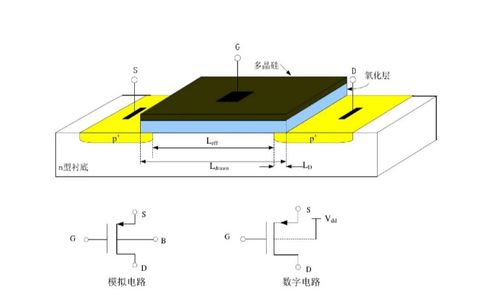

在CMOS工藝中,虛零點常通過跨導(dǎo)級之間的信號前饋路徑或電容電阻網(wǎng)絡(luò)來主動實現(xiàn)。例如,在一個兩級運放中,第一級(輸入級)的輸出信號可以通過一個小的電容Cc(米勒補(bǔ)償電容)前饋到第二級(輸出級)的輸入節(jié)點,從而在傳遞函數(shù)中引入一個右半平面的零點。這個零點的頻率位置通常由跨導(dǎo)和補(bǔ)償電容決定(\(z = g{m2}/Cc\),其中\(zhòng)(g_{m2}\)是第二級的跨導(dǎo))。

虛零點法的優(yōu)勢與挑戰(zhàn)

主要優(yōu)勢:

1. 擴(kuò)展帶寬:通過抵消主極點的作用,可以有效提升放大器的單位增益帶寬。

2. 改善建立時間:對于階躍響應(yīng),合理配置的虛零點可以減少過沖,優(yōu)化建立時間,這對高速高精度數(shù)據(jù)轉(zhuǎn)換器至關(guān)重要。

3. 設(shè)計靈活性:為零點頻率的調(diào)整提供了額外的自由度,使設(shè)計師能在穩(wěn)定性、帶寬和功耗之間取得更優(yōu)的平衡。

面臨挑戰(zhàn):

1. 精確控制:零點頻率對工藝、電壓、溫度(PVT)變化敏感,需要穩(wěn)健的設(shè)計或額外的校準(zhǔn)電路。

2. 潛在風(fēng)險:如果零點頻率過低,反而會嚴(yán)重惡化相位裕度,導(dǎo)致振蕩。因此,其位置必須被精確“放置”在頻率域的高于單位增益頻率的區(qū)域,使其負(fù)面影響最小化,而利用其有益的相位貢獻(xiàn)。

3. 增加復(fù)雜度:引入前饋路徑可能會增加芯片面積、功耗或噪聲。

在集成電路設(shè)計中的典型應(yīng)用

- 兩級運算放大器:這是虛零點法最經(jīng)典的應(yīng)用場景。采用米勒補(bǔ)償并帶有調(diào)零電阻(在補(bǔ)償電容Cc上串聯(lián)一個電阻Rz)的結(jié)構(gòu),是抵消右半平面零點甚至將其移動到左半平面,或?qū)⑵滢D(zhuǎn)化為一對復(fù)零點以優(yōu)化瞬態(tài)響應(yīng)的標(biāo)準(zhǔn)技術(shù)。這里的Rz用于調(diào)整前饋路徑的等效阻抗,從而精確控制零點位置。

- 帶隙基準(zhǔn)源:在提高電源抑制比(PSRR)的環(huán)路中,有時會利用虛零點概念來補(bǔ)償環(huán)路增益,確保在全頻段內(nèi)的穩(wěn)定性。

- 高階濾波器:在連續(xù)時間濾波器中,為了精確實現(xiàn)傳遞函數(shù)并保證穩(wěn)定性,設(shè)計師可能需要主動合成包括虛零點在內(nèi)的特定零極點圖。

設(shè)計考量與未來趨勢

在現(xiàn)代深亞微米CMOS工藝下,電源電壓不斷降低,晶體管的本征增益下降,使得多級放大器的頻率補(bǔ)償更具挑戰(zhàn)性。虛零點法及其衍生技術(shù)(如電流緩沖器米勒補(bǔ)償、多通路嵌套米勒補(bǔ)償?shù)龋┳兊酶又匾TO(shè)計師需要借助先進(jìn)的仿真工具,進(jìn)行細(xì)致的交流、噪聲和瞬態(tài)分析,并充分考慮PVT角(Corner)下的性能。

隨著電路向更高速度、更低功耗和更復(fù)雜系統(tǒng)集成方向發(fā)展,對虛零點等高級補(bǔ)償技術(shù)的理解和創(chuàng)新應(yīng)用,仍將是模擬與混合信號集成電路設(shè)計師必備的核心技能之一。掌握其精髓,意味著能在嚴(yán)格的約束條件下,挖掘出CMOS工藝的性能極限,創(chuàng)造出更卓越的芯片。